efficient test response compression for multiple-output circuits|Efficient test response compression for multiple : factories This paper describes a test response compaction method that preserves diagnostic information and enables performing a test-per-clock offline test. The test response . Resultado da Este site oferece jogos com uma experiência de aventura. Para ser um usuário do nosso site, você deve ter pelo menos 18 anos. Não somos responsáveis por violar suas leis locais relacionadas a jogos online.

{plog:ftitle_list}

23 de jan. de 2022 · Golpistas mandam e-mail falso para comprovar venda em site e usam serviços de entregas por aplicativo para buscar os produtos. Em novo episódio do quadro 'É Golpe?', saiba como se proteger.

We then introduce several systematic design techniques that guarantee zero-aliasing compression for single stuck-line faults in multiple-output circuits. We present the results of applying this approach to the ISCAS combinational benchmark circuits using both reduced and .

Proceedings of the IEEE International Test Conference on TEST: The Next 25 Years; Efficient Test-Response Compression for Multiple-Output Cicuits; Article . Free Access. Share on. .

Tutorial Survey of Test Vector Compression Techniques

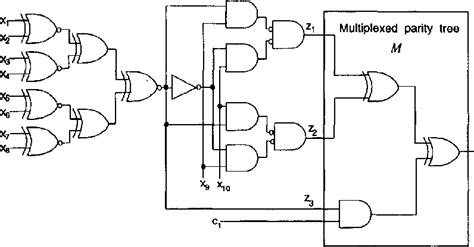

Test response compaction using multiplexed parity trees

This work introduces several systematic design techniques that guarantee zero-aliasing compression for single stuck-line faults in multiple-output circuits and shows that very high . This paper describes a test response compaction method that preserves diagnostic information and enables performing a test-per-clock offline test. The test response .Three general approaches help overcome this bottle-neck: stand-alone BIST, hybrid BIST, and test data com-pression. Stand-alone BIST. Traditional stand-alone BIST involves using on .Chandraet al.[20] introduced an efficient scan test compression technique called Zscan which reduces scan test channels. Zscan needs additional registers to convert a few inputs to .

This work introduces several systematic design techniques that guarantee zero-aliasing compression for single stuck-line faults in multiple-output circuits and shows that .The idea is to store the test vectors for a core in the tester memory in compressed form, and then transfer the compressed vectors to the chip, where a small amount of on-chip circuitry . We then introduce several systematic design techniques that guarantee zero-aliasing compression for single stuck-line faults in multiple-output circuits. We present the .Efficient test response compression for multiple-output circuits; Article . Free Access. Share on. Efficient test response compression for multiple-output circuits. Authors: Krishnendu .

A major obstacle to achieving high fault coverage in built-in self testing (BIST) methods that employ response compression is aliasing, which occurs when a faulty circuit's signature maps to the fault-free signature. Another problem with many compression methods is that they are inefficient for multiple-output circuits. We present data showing that in most .Test costs for large industrial designs increase rapidly in recent years. On-chip test compression hardware has become a pragmatic technology to cut down the overall test costs by reducing the test data volume. Determining the input and output channel counts of test compression hardware that results in minimum test data volume is thus a critical issue. In this article, .This paper presents results on fault simulation and response compaction on ISCAS 89 full scan sequential benchmark circuits using HOPE-a fault simulator developed for synchronous sequential circuits that employs parallel fault simulation with heuristics to reduce simulation time in the context of designing space-efficient support hardware for built-in self-testing of very .

A major obstacle to achieving high fault coverage in built-in self testing (BIST) methods that employ response compression is aliasing, which occurs when a faulty circuit's signature maps to the fault-free signature. Another problem with many compression methods is that they are inefficient for multiple-output circuits. We present data showing that in most cases, faults .Efficient test response compression for multiple-output circuits; Article . Free Access. Share on. Efficient test response compression for multiple-output circuits. Authors: Krishnendu Chakrabarty. Advanced Computer Architecture Laboratory, Department of Electrical Engineering and Computer Science, University of Michigan, Ann Arbor, MI . The objective of this research is the assessment of circuit design compression strategy carrying a greater number of similar output chains. The proposed method decreases the testing time while .

Index Terms—Data compression, floating-point number, quan-tization, the prediction method, transient simulation waveform. I. INTRODUCTION TRANSIENT circuit simulation has become one of the most important steps in the design of analog or mixed-signal integrated circuits. Its output is voltage waveforms for A highly efficient SOC test compression scheme which uses sequential linear decompressors local to each core is proposed. Test data is stored on the tester in compressed form and brought over the . Test compression builds on technology originally developed for LBIST (logic built-in self-test). Figure 1 shows the general structure of compression logic within a chip or core. The system decompresses a compressed input stream and feeds it into the internal scan chains, some of which may be inside cores within the design. We present a technique for compacting test response data using combinational logic circuits. Our compaction technique enables up to an exponential reduction in the number of pins required to .

Test response compaction method with improved detection and

The chapter focuses on test stimulus compression and describes three different categories of schemes: using data compression codes, employing linear decompression, and broadcasting the same value to multiple scan chains. Moreover some additional on-chip hardware before the scan chains to decompress the test stimulus coming from the tester and . Efficient methods to estimate test pattern counts for an extensive range of input/output counts are developed and require only a small number of ATPG runs to determine the test data volume for each input/ Output configuration. Test costs for large industrial designs increase rapidly in recent years. On-chip test compression hardware has become a .This is due to its compactness, high compression rate and adoptability to circuits with multiple scan chains. As a space compression method, an XOR network is typically used to compress the output response [4]. Unknown values are often seen in the output response of a circuit during logic and fault simulation [17].method for test data compression based on Iterative XOR Matrix. The main idea behind this method is to perform effective data compression to the requirement of the tester using the functionality of XOR gate. 2. PROPOSED COMPRESSION TECHNIQUE The proposed test data compression technique is based on using XOR gates in an iterative fashion at

Enter the email address you signed up with and we'll email you a reset link. For more information, see the IANA Official Content Coding List.. The response compression middleware allows adding additional compression providers for custom Accept-Encoding header values. For more information, .

It is shown that given a precomputed test set T , the test responses at the functional outputs of the given circuit-under-test (CUT) can be compacted to a single periodic output, with guaranteed .

This work describes a simple but cost-effective solution called channel masking that masks the X-states and allows test compression methods to be widely deployed on a variety of designs.This paper focus on the design of Programmable MISR(Multiple Input Signature Register) modules for Logic BIST based Very Large Scale Integration(VLSI) Integrated Circuit(IC) testing. The advancement in VLSI technology have made chip testing more complicated which has lead to the popularity of Logic Built In Self Test(LBIST) compared to Automatic Test Equipment(ATE). . The measurement results of a test circuit show its relatively high current efficiency of 74 and 99.93% for output current 100 µA and 50 mA, respectively. The output voltage overshoot and undershoot are below 46 and 75 mV for output current change from 0.1 to 50 mA with the rise and fall times equal to 0.3 µs, and load capacitance 0–100 pF.The procedure is based on reseeding of the LFSR to mask unknown output values while allowing fault effects to propagate, and to determine the seeds, the output response of the circuit is partitioned into a minimal number of fragments. We propose a procedure for designing an LFSRbased circuit for masking of unknown output values that appear in the output .

(ATPG-generated) test set to the circuit under test (CUT). Survey of Test Vector Compression Techniques Test data compression consists of test vector compression on the input side and response compaction on the output side. Test vector compression has been an active area of research, yielding a wide variety of techniques. This This paper proposes a cascaded multicasting scan (CMS) architecture with simple control logic and low hardware overhead for test data compression. Instead of specifying all the addresses of the scan chains that will receive the test data in each broadcast, CMS specifies only the address of the first scan chain using log2(n) control bits in each broadcast on an n-scan .and the IF output is a fixed amount of compression. Mini-Circuits specifies the typical RF input power at the 1-dB compression point, where conversion loss is 1 dB greater than it is at low RF power. Naturally, if an application allows a greater amount of compression, the acceptable RF input power would be higher.

Two efficient output selection algorithms are presented to determine the desired output responses, one using a single counter operation for simpler test control and the other using more counter .

IEEE TRANSACTIONS ON COMPUTER

A new test data compression method using Transition Directed Run-length code (TDR) is proposed. The proposed method is suitable for encoding the test set for embedded cores in a system-on-a-chip.The data is plotted, here using Microsoft Excel, and compression points are picked off the graph. The figure below shows an example of the input/output characteristic of an amplifier measured this way (actual measured data, taken using our power meter measurement setup). The measured output power is plotted against the ideal linear response.

Efficient test response compression for multiple

Efficient Test

(PDF) An efficient test vector compression scheme using

A new team of superhuman power rangers must work together and use their new ninja powers to prevent evil from dominating the human race and from destroying the planet earth and the universe. Stars: William Shewfelt, Nico Greetham, Zoë Robins, Peter Adrian Sudarso. Votes: 1,140. All Power Rangers Series.

efficient test response compression for multiple-output circuits|Efficient test response compression for multiple